# Final project report: Mixed analog and digital integrated circuits

## **Project leaders**

Prof. Mark Vesterbacka, Linköping University Dr. J. Jacob Wikner, Infineon Technologies AB

# Duration

The project started 1 Jan. 1999, and ended 31 Dec. 2004.

# **Research** area

The current trend within electronics research is to solve problems related to System-on-Chip (SoC), where the ultimate goal is to put all electronics in a product on a single silicon chip. Achieving this goal would significantly reduce cost and power consumption of a product, while the reliability and performance would increase. With the rapidly increasing integration of circuits on silicon chips already taking place, there are mainly two major problems remaining that need to be addressed. One problem is to handle the complexity within the design of large systems. The other problem is to integrate analog and digital circuits on the same chip. In this project we have mainly focused on the latter problem.

#### **Major achievements**

The main achievement during the first year (1999) was the invention of a new method to interface the digital parts to the analog synthesizer in a digital-to-analog (DA) converter [3, 4, 6]. Use of this method reduces the glitch noise, which is a serious problem in high-speed or oversampling DA converters. Prior methods aiming at solving this particular problem has all suffered from that the design complexity becomes unmanageable for high resolutions (e.g. 10-bit DA converters). Our method does not suffer from this. It should be appropriate for, e.g., 14-bit high-speed DA converters. This invention resulted in a patent [42].

During the second year (2000) we have developed an encoding algorithm for the method above. The hardware has been designed for a 14-bit encoder, which seems to be sufficiently small for practical use [10]. Also, several ideas have come up as "side effects" from the approach above. One of the new ideas uses a special coding to reduce errors induced in the analog domain with digital signal processing [8, 9]. This invention did also lead to a patent [44].

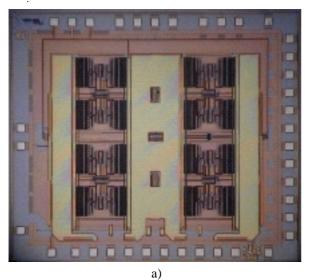

During the third project year (2001) we have developed our invention from 1999 so that the glitch noise spectrum is shaped to yield a low relative error [12]. Comparing with prior methods, the results indicate a significant improvement in the relative error. We have also made improvements to the hard-ware for the encoding algorithm. As a "side effect" of this work we have demonstrated a new square root approximation technique with less latency than prior methods. A very interesting result is that we have been able to extend this technique to implementation of fast division [36], which so far generally has been avoided in DSP hardware due to the long computational latency. We evaluated a technique for enhanced static performance of DA converters and obtained good results from measurements of a test chip, shown in Fig. 1 a). We did also perform simulations that showed limited efficiency of using the technique in the presence of dominating dynamic errors [14, 20].

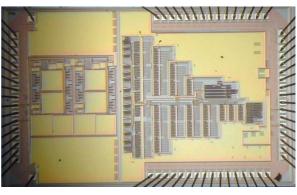

During the fourth project year (2002), project leader M. Vesterbacka became full professor in Electronics Systems, and the first licentiate thesis was presented in Nov. [21]. We have designed a mixed-signal test circuit consisting of an analog filter used for estimating analog performance and a digital filter block for which a number of parameters can be controlled [16, 19, 23]. With this experiment we are able to evaluate the effect of digital noise injected into the analog parts in an actual implementation [25, 28, 34], and how different techniques reduce the noise. A photograph of the fabricated test circuit is shown in Fig. 1 b). We have also designed a second chip with two on-chip DA-converters that can be configured into a number of experiments involving signal processing to improve the performance [15], Fig. 1 c). A study on mixed-signal circuits implemented in silicon-on-insulator (SOI) technology [26] was initiated during the second half of 2002.

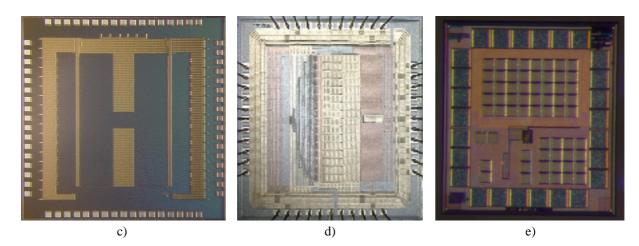

During the fifth year (2003), a new method of coding the control signals in DA converters aiming at low glitches and high linearity was developed. A test chip for evaluation of the new code was developed and has since then been measured [27, 29, 32]. The new code performance yields similarly good performance as the invention from 1999, but with a considerably lower complexity of the required encoding hardware. The chip photograph is shown in Fig. 1 d). Other work performed is the characterization of the noise injection test chip above where the digital part has been fully characterized and we are currently finalizing the characterization of the analog part. Our first circuit implemented in SOI technology, a high speed comparator, was designed.

During the sixth and final project year (2004), the SOI comparator was manufactured and measured, which in large worked as expected [33]. The chip is shown in Fig. 1 e). This circuit was used as the base for the design of two different 6-bit flash AD converters in SOI technology. The first design employs a new, fast type of digital decoder that should obtain a sampling frequency above 1 GHz [31, 35]. The second design includes an innovative control of the voltage reference that will linearize the transfer characteristics of the converter [31]. The designs have been completed and will be manufactured during early 2005. During the spring 2005, the first dissertation within the project will be defended, as well as the second licentiate thesis.

b)

Fig. 1. Chips manufactured during the project:

- a) 14-bit DA converter with 40 MS amples/s conversion speed using a special linearization technique,

- b) test chip for evaluation of the effect of digital noise injected into analog circuits,

- c) dual 14-bit DA converter for on-line calibration improving the dynamic performance,

- d) 12-bit reconfigurable DA converter employing a new coding technique, and

- e) comparator for use in a future 1 GHz, 6-bit flash ADC, implemented in a new type of technology.

# **Research group**

A stated long-term goal with this project was to create a strong research group within the area of mixedsignal circuits. During the project time, the group has developed to currently include seven members. Besides the project leaders the group we have an industrial mentor, Dr. Mikael Rudberg, whom also have participated in our research projects [8, 9, 47], and the four graduate students Lic.Eng. K. Ola Andersson [1, 7, 11, 14, 15, 17, 18, 20, 21, 22, 27, 29, 30, 31, 32, 38, 40, 42], M.Sc. Niklas U. Andersson [2, 5, 8, 9, 11, 14, 15, 17, 18, 20, 21, 22, 44], M.Sc. Erik Backenius [16, 19, 23, 25, 28, 34], and M.Sc. Erik Säll [24, 26, 30, 31, 33, 35]. The group has supervised and examined about 60 final projects, approximately equally distributed on master and bachelor thesis works. Nine of the master theses were directly related to this project.

# Cooperation

During the project, we have had good contact with Ericsson Microelectronics, which supported the continued project participation of leader Dr. J.J. Wikner and Dr. student N.U. Andersson after they had been employed by the company. Ericsson Microelectronics became a part of Infineon Technologies in 2002. Our cooperation has included project discussions, design reviews, and we have also been able to use Infineon's measurement laboratory for measuring our fabricated chips. While the actual designs carried out within the project has not been used in products, the ideas and concepts developed in the project have been integrated into the design flow at the Linköping branch of Infineon Technologies. We have also planned a common project where our group should investigate the substrate noise of some Infineon designs. Besides the cooperation with Infineon, we have also supervised a number of final projects for the companies Aerotech Telub, Ericsson Access, Ericsson Microelectronics, Ericsson Mobile Communications, Epact Technology, Image Systems, Sectra, SiCon, the Swedish Defence Research Agency (FOI), and Zarlink Semiconductor.

Within CENIIT we have recently had discussions on cooperating with the new CENIIT-project 04.07 *Flexible Frequency-band Reallocation* managed by Dr. P. Löwenborg, ISY. A possible outcome of the future cooperation would be research on how to improve the performance of AD converters with signal processing by exploiting new inventions and findings.

## **Support**

During the project time we have received a total of 2 890 kSEK in financial support from CENIIT. Approximately 40% of this amount was spent on partially financing the salary of the project leader M. Vesterbacka, 30% was used to support the salary of Dr. student K. O. Andersson, and 6% was spent on design support contributions by "ammanuens" P. Lander, Dr. student E. Hjalmarsson, and research engineer G. Karlströms. The remaining 24% was used for costs like travel, copying, telephone, and other costs common to the department of Electrical Engineering.

## **Publications**

- [1] K.O. Andersson and J.J. Wikner, "Modeling of the Influence of Graded Element Matching Errors in CMOS Current-Steering DACs," *Proc. Norchip Conf.*, Oslo, Norway, Nov. 8-9, 1999.

- [2] N.U. Andersson and J.J. Wikner, "Comparison of Different Dynamic Element Matching Techniques for Wideband CMOS DACs," Proc. Norchip Conf., Oslo, Norway, Nov. 8-9, 1999.

- [3] J.J. Wikner and M. Vesterbacka, "D/A Conversion with Linear-Coded Weights," *Proc. 2000 Southwest Symp. on Mixed-Signal Design*, pp. 61-66, San Diego, California, Feb. 27-29, 2000.

- [4] J.J. Wikner and M. Vesterbacka, "Characteristics of Linear-Coded D/A Converters," *Proc. 2000 Southwest Symp. on Mixed-Signal Design*, pp. 67-72, San Diego, California, Feb. 27-29, 2000.

- [5] N.U. Andersson and J.J. Wikner, "A Strategy of Implementing Dynamic Element Matching in Current-Steering DACs," *Proc. 2000 Southwest Symp. on Mixed-Signal Design*, pp. 51-56, San Diego, Feb. 27-29, 2000.

- [6] M. Vesterbacka and J.J. Wikner, "Dual Matrix Linear-Code D/A Converters," *Proc. 2000 IEEJ Int. Analog VLSI Workshop*, pp. 63-68, Stockholm, Sweden, June 2-3, 2000.

- [7] K.O. Andersson and J.J. Wikner, "Characterization of a CMOS Current-Steering DAC using State-Space Models," *Proc. 2000 IEEE Midwest symposium on circuits and systems*, MWSCAS'2000, Michigan, Aug. 8-11, 2000.

- [8] M. Vesterbacka, M. Rudberg, J.J. Wikner, and N.U. Andersson, "Dynamic Element Matching in D/A Converters with Restricted Scrambling", *IEEE Proc. The 7th Int. Conf. on Electronics, Circuits, and Systems*, ICECS'00, vol. 1, pp. 36-39, Beirut, Lebanon, Dec. 17-20, 2000.

- [9] M. Rudberg, M. Vesterbacka, N.U. Andersson, and J.J. Wikner, "Glitch Minimization and Dynamic Element Matching in D/A Converters," *IEEE Proc. The 7th Int. Conf. on Electronics, Circuits, and Systems*, ICECS'00, vol. 2, pp. 899-902, Beirut, Lebanon, Dec. 17-20, 2000.

- [10] M. Vesterbacka and J.J. Wikner, "Design of Encoders for Linear-Coded D/A Converters," Proc. 2001 IEEE Int. Symp. on Circuits and Systems, ISCAS'01, vol. 1, pp. 524-527, Sydney, Australia, May 6-9, 2001.

- [11] K.O. Andersson, N.U. Andersson, and J.J. Wikner, "Spectral shaping of DAC nonlinearity errors through modulation of expected errors," *Proc. IEEE Int. Symp. on Circuits and Systems*, ISCAS'01, vol. 3, pp. 417-420, Sydney, Australia, May 6-9, 2001.

- [12] M. Vesterbacka, "Linear-Coded D/A Converters with Small Relative Error Due to Glitches," Proc. IEEE Midwest Symp. on Circuits and Systems, MWSCAS'01, vol. 1, pp. 280-283, Fairborn, Ohio, Aug. 14-17, 2001.

- [13] Y. Gao, J.J. Wikner, and H. Tenhunen, "Design and Analysis of an Oversampling D/A Converter in DMT-ADSL Systems," *Kluwer Int. J. of Analog Integrated Circuits and Signal Processing*, vol. 32, no. 3, pp. 201-210, Sept. 2002.

- [14] N.U. Andersson, K.O. Andersson, M. Vesterbacka, and J.J. Wikner, "Models and Implementation of a Dynamic Element Matching DAC," *Proc. IEEE The Nordic Event in ASIC Design Conf.*, NORCHIP'01, pp. 155-160, Stockholm, Sweden, Nov. 12-13, 2001.

- [15] K.O. Andersson, N.U. Andersson, M. Vesterbacka, and J.J. Wikner, "A Differential DAC Architecture with Variable Common-Mode Level," *Proc. IEEE Int. Symp. on Circuits and Systems*, ISCAS'02, vol. 1, pp. 113-116, Scottsdale, Arizona, USA, May 26-29, 2002.

- [16] E. Backenius, M. Vesterbacka, and R. Hägglund, "Reduction of Clock Noise in Mixed-Signal Circuits," *Proc. National Conf. on Radio Science*, RVK'02, Stockholm, Sweden, June 10-13, 2002.

- [17] K.O. Andersson, N.U. Andersson, M. Vesterbacka, and J.J. Wikner, "Combining DACs for Improved Performance," Proc. 4th IEE Int. Conf. on Advanced A/D and D/A Conversion Techniques and Their Applications, Prague, Czech Republic, June 26-28, 2002.

- [18] M. Vesterbacka, K.O. Andersson, N.U. Andersson, and J.J. Wikner, "Using Different Weights in DACs for Improved Performance," Proc. 4th IEE Int. Conf. on Advanced A/D and D/A Conversion Techniques and Their Applications, Prague, Czech Republic, June 26-28, 2002.

- [19] E. Backenius, M. Vesterbacka, and R. Hägglund, "A Strategy for Reducing Clock Noise in Mixed-Signal Circuits," Proc. IEEE Midwest Symp. Circuits and Systems, MWSCAS'02, Tulsa, Oklahoma, Aug. 2002.

- [20] N.U. Andersson, K.O. Andersson, J.J. Wikner, and M. Vesterbacka, "Models and Implementation of a Dynamic Element Matching DAC," *Kluwer Int. J. of Analog Integrated Circuits and Signal Processing*, vol. 34, no. 1, pp. 7-16, Jan. 2003.

- [21] K.O. Andersson, N.U. Andersson, M. Vesterbacka, and J.J. Wikner, "A Method of Segmenting Digital-to-Analog Converters," *Proc. IEEE Southwest Symp. Mixed-Signal Design*, pp. 32-37, Las Vegas, NV, USA, Feb. 2003.

- [22] K.O. Andersson, N.U. Andersson, M. Vesterbacka, and J.J. Wikner, "A 14-bit Dual Current-Steering DAC," Proc. Swedish System-on-Chip Conf. 2003, Eskilstuna, Sweden, Apr. 2003.

- [23] E. Backenius and M. Vesterbacka, "Characteristics of a Differential D flip-flop," *Proc. Swedish System-on-Chip Conf. 2003*, Eskilstuna, Sweden, Apr. 2003.

- [24] E. Säll, "A 1.8V 10-bit 80MS/s Low Power Track-and-Hold Circuit in a 0.18 μm CMOS Process," Proc. IEEE Int. Symp. on Circuits and Systems, Bangkok, Thailand, May 2003.

- [25] E. Backenius and M. Vesterbacka, "A Digital Circuit with Relaxed Clocking," Proc. Swedish System-on-Chip Conf. 2004, Båstad, Sweden, Apr. 13-14, 2004.

- [26] E. Säll and M. Vesterbacka, "Silicon-on-Insulator CMOS Technology for System-on-Chip," Proc. Swedish System-on-Chip Conf. 2004, Båstad, Sweden, Apr. 13-14, 2004.

- [27] K.O. Andersson and M. Vesterbacka, "A Testbed for Different Codes in Digital-to-Analog Converters," Proc. Swedish System-on-Chip Conf. 2004, Båstad, Sweden, Apr. 13-14, 2004.

- [28] E. Backenius and M. Vesterbacka, "Design of Circuits for a Robust Clocking Scheme," Proc. IEEE Mediterranean Electrotechnical Conf., MELECON'04, vol. 1, pp. 185-188, Dubrovnik, Croatia, May 12-15, 2004.

- [29] K.O. Andersson and M. Vesterbacka, "Partial Decomposition of Digital-to-Analog Converters," *Proc. IEEE Mediterranean Electrotechnical Conf.*, MELECON'04, vol. 1, pp. 193-196, Dubrovnik, Croatia, May 12-15, 2004.

- [30] E. Säll, M. Vesterbacka, and K.O. Andersson, "A Study of Digital Decoders in Flash Analog-to-Digital Converters," 2004 IEEE Int. Symp. on Circuits and Systems, ISCAS'04, vol. 1, pp. 129-132, Vancouver, Canada, May 23-26, 2004.

- [31] E. Säll, K.O. Andersson, and M. Vesterbacka, "A Dynamic Element Matching Technique for Flash Analogto-Digital Converters," *Proc. 2004 IEEE Nordic Signal Processing Symp.*, NORSIG'04, Espoo, Finland, June 9-11, 2004.

- [32] K.O. Andersson and M. Vesterbacka, "A Parameterized Cell-Based Design Approach for Digital-to-Analog Converters," *Proc. IEEE 4th Int. Workshop on System-on-Chip for Real-Time Applications*, IWSOC'04, pp. 225-228, Banff, Alberta, Canada, July 19-21, 2004.

- [33] E. Säll and M. Vesterbacka, "Design of a Comparator in CMOS SOI," Proc. IEEE 4th Int. Workshop on System-on-Chip for Real-Time Applications, IWSOC'04, pp. 229-232, Banff, Alberta, Canada, July 19-21, 2004.

- [34] E. Backenius and M. Vesterbacka, "Evaluation of a Clocking Strategy with Relaxed Constraints on Clock Edges," *Proc. IEEE Analog and Digital Techniques in Electrical Engineering*, TENCON'04, Chiang Mai, Thailand, Nov. 21-24, 2004.

- [35] E. Säll and M. Vesterbacka, "A Multiplexer Based Decoder for Flash Analog-to-Digital Converters," Proc. IEEE Analog and Digital Techniques in Electrical Engineering, TENCON'04, Chiang Mai, Thailand, Nov. 21-24, 2004.

### Thesis

[36] K.O. Andersson, Studies on Performance Limitations in CMOS DACs, Licentiate Thesis No. 976, LiU-Tek-Lic-2002:49, Linköping University, Nov. 2002. ISBN 91-7373-452-7.

#### **Related publications**

- [37] J.J. Wikner and N. Tan, "Modeling of CMOS Digital-to-Analog Converters for Telecommunication," *IEEE Trans. on Circuits and Systems II*, May, 1999.

- [38] M. Vesterbacka, "A Robust Differential Scan Flip-Flop," *Proc. IEEE Int. Symp. on Circuits and Systems*, vol. I, pp. 334-337, Orlando, Florida, May 30 June 2, 1999.

- [39] M. Vesterbacka, "A Static CMOS Master-Slave Flip-Flop Experiment", *IEEE Proc. The 7th Int. Conf. on Electronics, Circuits, and Systems*, Beirut, Lebanon, Dec. 17-20, 2000.

- [40] R. Hägglund, P. Löwenborg, and M. Vesterbacka, "A Polynomial-Based Division Algorithm," Proc. 2002 IEEE Int. Symp. on Circuits and Systems, ISCAS'02, Phoenix, Arizona, May 24-29, 2002.

- [41] M. Karlsson and M. Vesterbacka, "A Non-Overlapping Two-Phase Clock Generator with Adjustable Duty Cycle," *Electronic Proc. Nat. Symp. on Microwave Technique and High Speed Electronics*, GHz'03, http://www.ep.liu.se/ecp/008/posters/002/, Linköping, Sweden, Nov. 4-5, 2003.

#### Patents

- [42] J.J. Wikner and M. Vesterbacka, "D/A Conversion Method and D/A Converter," Swedish patent 9903500-8, Oct. 1999. U.S. patent, Oct. 2000.

- [43] K.O. Andersson, "Improved current-steering D/A conversion," Swedish patent 0000731-0, 2000.

- [44] N.U. Andersson, M. Vesterbacka, J.J. Wikner, and M. Rudberg, "Improvement of segmented DACs", Swedish patent 0001917-4, May 2000. U.S. patent.

- [45] K.O. Andersson, "Current Steering DAC," pending Swedish patent 0101513-0, April 2001.

- [46] K.O. Andersson and J.J. Wikner, "Digital-to-Analog Converter Having Error Correction," *pending Swedish patent*, 2002.

#### Tutorial

[47] M.K. Rudberg, J.-E. Eklund, J.J. Wikner, and J. Elbornsson, "A/D and D/A Converters for Telecom," tutorial IEEE 7th Int. Conf. on Electronics, Circuits, and System, ICECS'01, Malta, Sept. 2, 2001.